NCR 725 / 605 Technology

The NCR 605 is a 16-bit CPU implemented entirely in small-scale integration TTL, mostly from the 7400 family. Such processors are unusual and date from a short period in the late 1960s-early 1970s. Designs of this type became possible when small-scale ICs became cheap and reliable at the end of the 1960s but were rapidly overtaken by the microprocessor revolution of the early 1970s.

Discrete IC CPUs remain interesting as they allow the entire processor to be seen and understood. Some current examples of this interest can be found at Magic-1 homepage and on the Home-built CPU Webring..

DoPECC is interested in the 605 for the same reason, its simple technology offers the opportunity to understand and restore an early 70s CPU that may then be kept running

The 605 was designed in-house at NCR in the late 1960s. According to one of those involved at the time, NCR did not want to expend resources on developing a new CPU and the 605 was developed under the cover story of being a peripheral controller for NCR’s Century-200 and -300 mainframes. It turned out to be a powerful and versatile processor and was used in a wide range of NCR products including

-

Mainframe Peripherals

- NCR 625 658 Disk Controllers

- NCR 721 755 Communication Controllers

-

Small Accounting machines

- NCR 399

- NCR 499

-

Standalone Computer Systems

- NCR 725 Retail Store Computer

- NCR Century 8200 System

Further very interesting first-hand information about the 605 and its associated systems can be found at Iain Simpson’s site. Recommended.

Restoring the 605 processor will be an interesting challenge and will require extensive data and documentation. Since the 605 was used in many NCR products some of which were sold in great numbers, it is hoped that there are engineers who have kept documents that they may be willing to share. Please send any information via the About/Contact link

CPU Architecture & Instruction Set

– research in progress –

Electronic Implementation

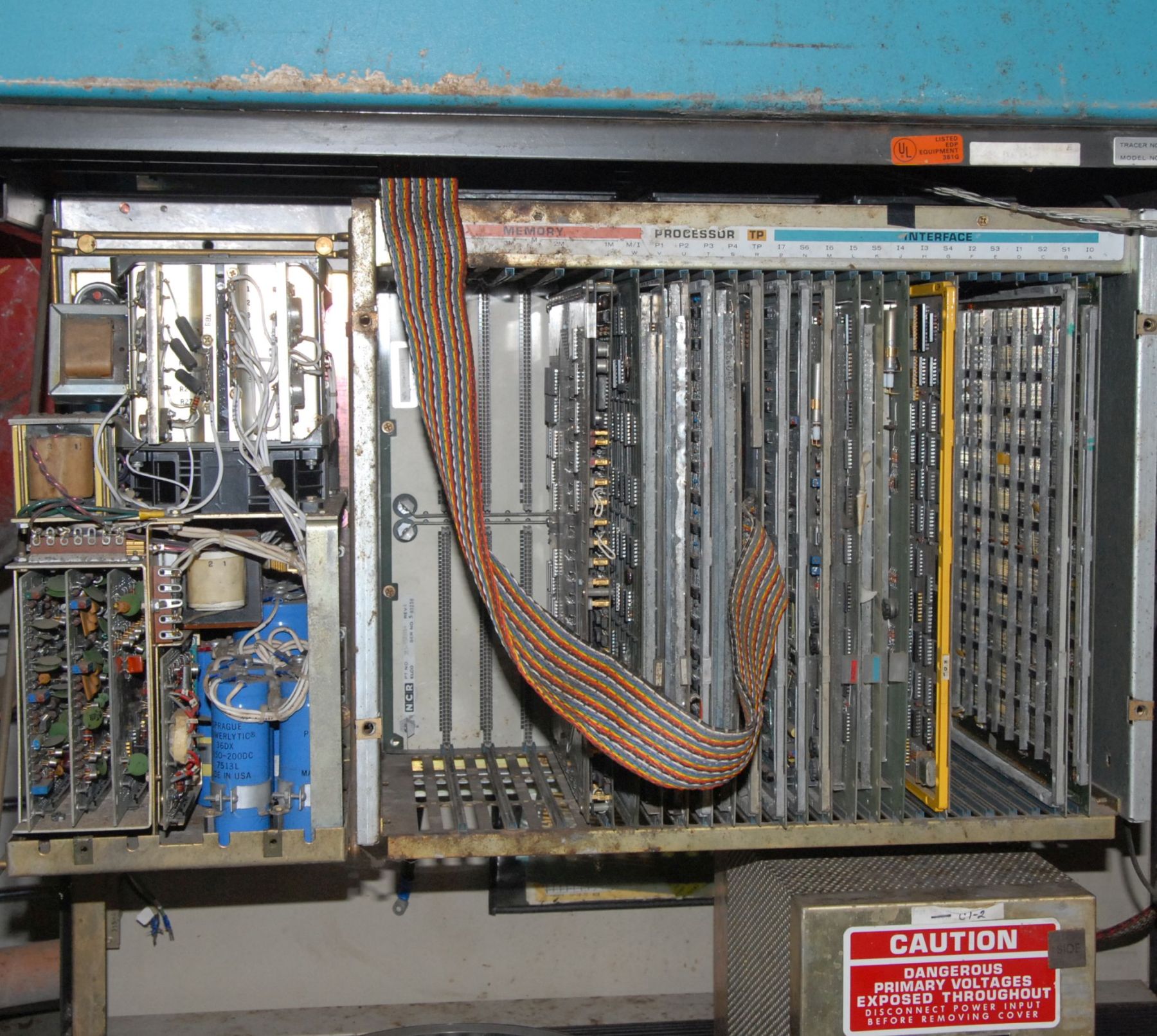

The processor is implemented in TTL ICs over 4 cards. Almost all ICs are 14pin gate and flip-flop level devices with just an handful of MSI devices that appear to be 4-16 decoders and the like, with nothing more sophisticated.

The cards are noteworthy for having heavy metal power bus flanges soldered to all power distribution traces and also for having far fewer supply bypass capacitors that would be expected today. The low impedence power distribution would have helped with noise but one wonders if the lack of more bypassing is a design deficiency.

It is also interesting to see that there are many circuit patches applied to all four cards. An original design engineer has commented that the design had many timing errors that had to be fixed in production, and the evidence is clear to see!

Control Panel

The control panel is wired to an interface card which is plugged into the backplane. Judging by the panel labels, it is possible to do far more than simply read and write memory. There is extensive monitoring of machine state (similar to early PDP-8 panels) and it also appears possible to modify internal state registers and counters.