Wang 600 Simple Microcode Emulator

Next Log Entry

Diagnostics with a 1-word emulator

Monitoring the ROM address input and data outputs showed that some microcode was executing but it was not possible to determine if the reason for no display was bad microcode from the ROM or bad logic in the execution engine.

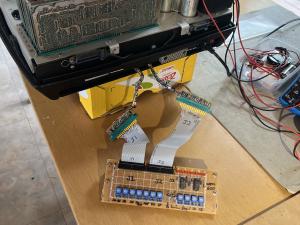

To assist with further testing a simple ROM emulator was constructed.

- a set of hex encoded switches to set a single 42-bit microcode word

- one switch per microcode field or digit

- 11 LEDs to monitor the address being presented to the ROM

- the ROM address is derived from the microcode word but may be modified by machine state

This simulator was substituted for the ROM and enabled a number of tests to be performed.

ROM Address Decoding from Microcode

-

Manually setting the JAD field caused the same data to appear on the ROM address lines, suggesting that the JAD part of the microcode address was being correctly propagated from ROM microinstructions to the ROM address register.

-

Setting 0x00 or 0x01 into JH and/or JL correctly cleared or set the two lowest order ROM address bits, suggesting that this part of the conditional address logic was working correctly.

MOP field

Most MOP field values have complex effects on internal states that are not straightforward to monitor. Some MOP combinations do have immediate, easy to detect effects:

- 1101 Tape motor on - confirmed with relay click

- 1110 Tape motor off - confirmed

ST Machine Status Control field

Most of these are difficult to monitor but some are easy:

- 1100 Set Overflow state and light - confirmed

- 1110 Set Error state and light - confirmed

ALU and Z0 Flag

A more complex test could be acheived in a single word by setting fields such that

- A- and B-bus inputs = 0

- ALU set to generate either

- A + B or

- A + B + 1

- next ROM address to be conditional on the state of Z0

The A + B instruction should give a zero result, set the Z0 condition bit and cause modification of the next address. A+B+1 should give a non-zero result, clearing the Z0 condition and leaving the next address unaltered. In each case the effect on the next address was observed to be correct.

While all of these results were encouraging, they also did not point to any reason for the general failure of the machine.

The true potential of this little device was overlooked. It turns out that one instruction is sufficient to test much more of the machine, and more progress could have been made with this device. See later posts for details

Previous Log Entry Back to Log Index Next Log Entry